Search Thermo Fisher Scientific

- Contact Us

- Quick Order

-

Don't have an account ? Create Account

Search Thermo Fisher Scientific

The Thermo Scientific nProber IV System is a high-performance scanning-electron-microscopy-based platform for the localization of transistor and metallization faults. It is our most advanced nanoprobing system to date, and the first to use the high-resolution LEEN2 SEM Column. The nProber IV System is specifically designed to increase the speed, accuracy, and output of your failure analysis (FA) workflow, where productivity is paramount.

The nProber IV System directly increases the success rate of transmission electron microscopy (TEM) analysis through precise fault localization and has proven to be both accurate and repeatable on even the most challenging process nodes. The automation and guided workflows of the nProber IV System improve lab productivity and allow your organization to focus on the output of your nanoprobing and TEM workflows while investing less in the operation of the system itself, thereby accelerating time-to-yield.

Time to yield is a significant focus for semiconductor fabs. The key to faster time to yield is the efficient identification of critical defects during process and device development. Nanoprobing plays a vital role in process yield ramp, localizing faults that cannot be found with other failure analysis techniques. Nanoprobing also delivers the precise localization required to ensure that the thin TEM samples will fully contain the fault, greatly improving the success rate of your TEM workflow. Finally, as nanoprobing localizes faults through accurate electrical characterization, TEM workflows that utilize nanoprobing combine TEM physical failure analysis with electrical fault signatures, helping to correlate process control improvements with device performance.

Thermo Fisher Scientific is the leader in supplying TEM workflows for process and device yield ramp, with widely adopted solutions for nanoprobing sample preparation, nanoprobing, TEM sample preparation and TEM physical failure analysis.

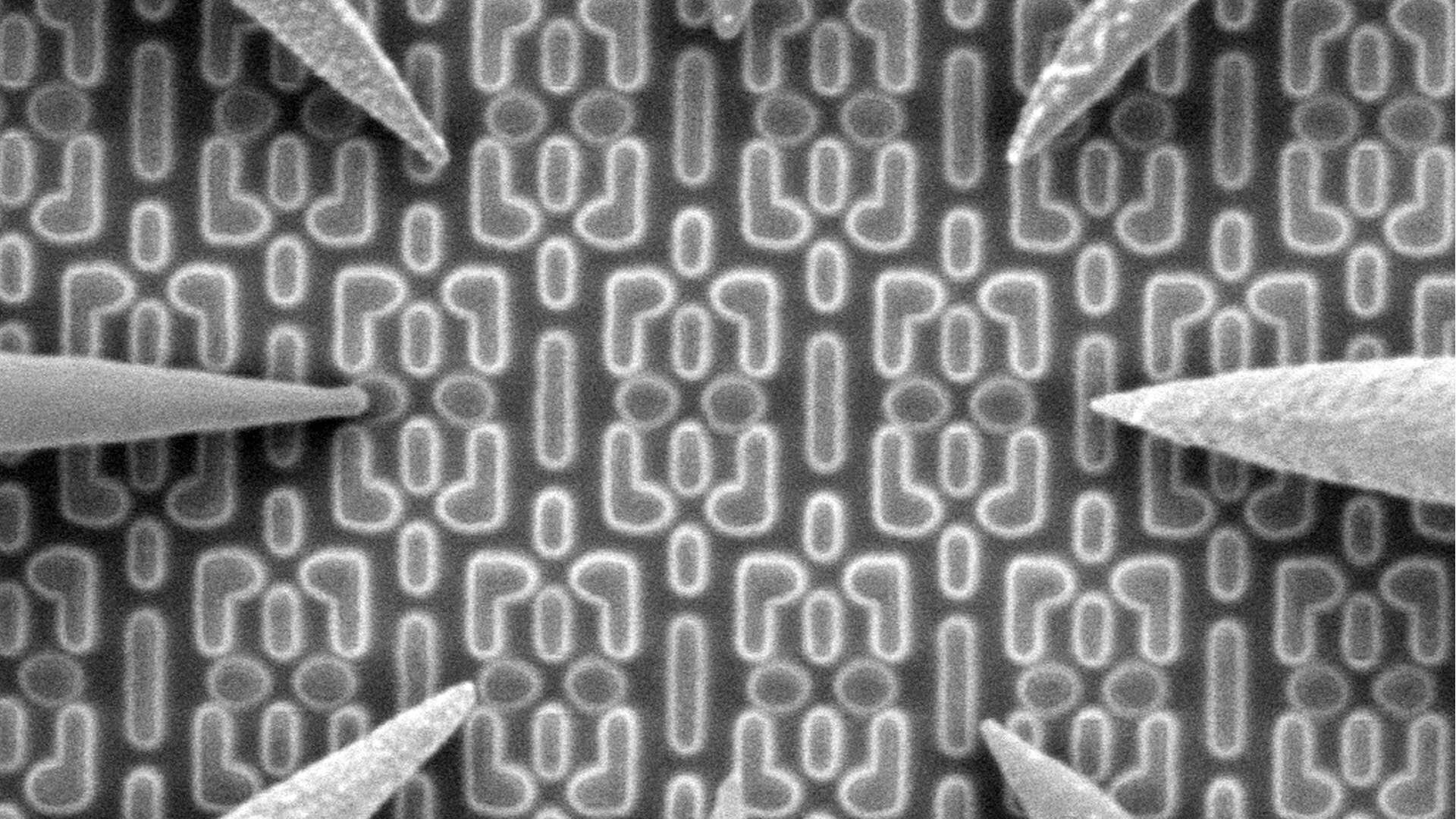

nProber IV SteadFast Nanomanipulators and temperature-controlled probing environment combine to give the probe the necessary stability for working with leading-edge transistors.

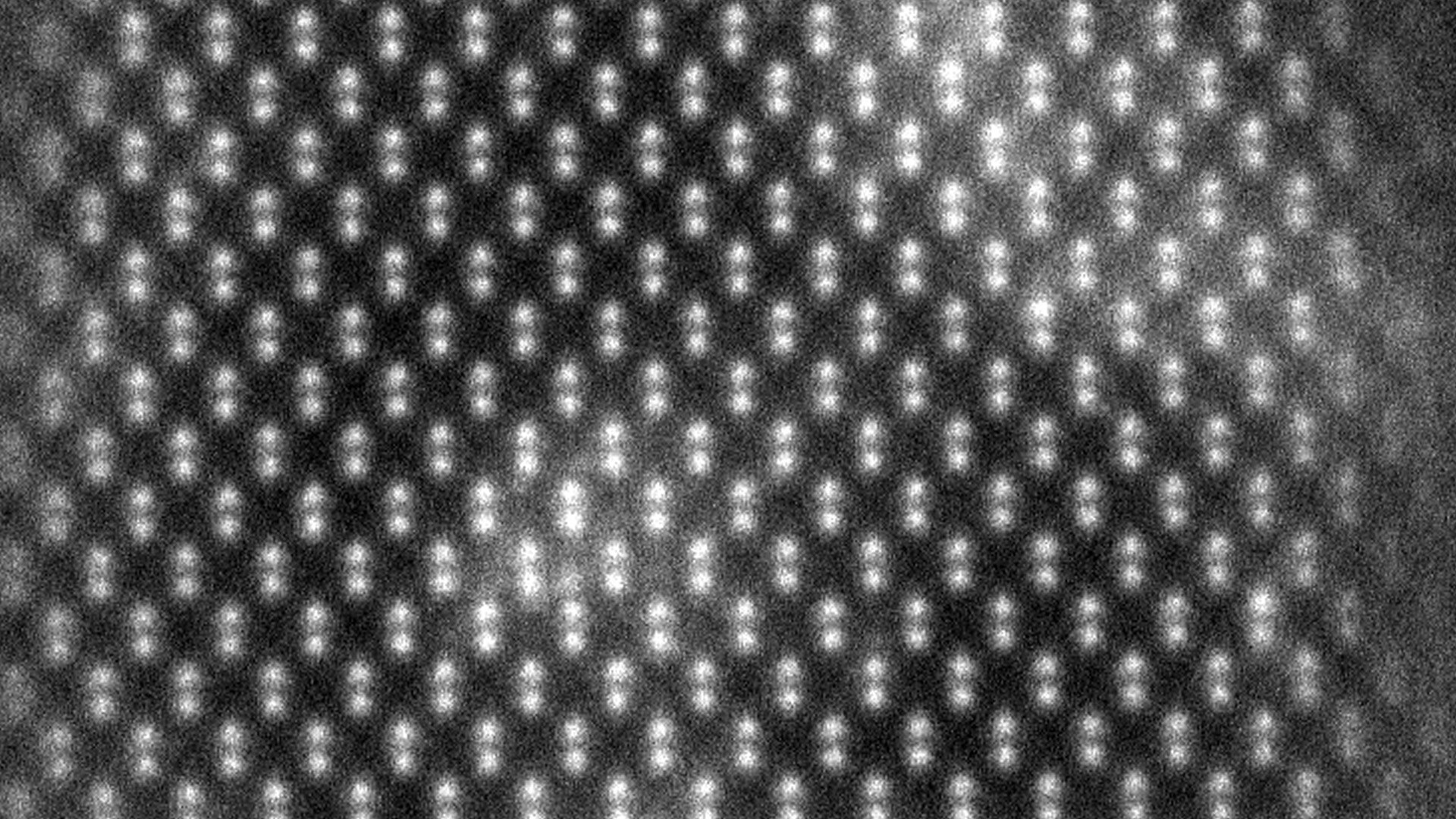

The new LEEN2 Column of the nProber IV System enables low eV imaging and probing operation and includes an advanced control system that reduces sample dose by up to 30%. These advances allow the nProber IV System to provide accurate measurements of critical transistor parameters with minimal shifts from SEM imaging.

The nProber IV System is equipped with eFast semi-automated guided workflows that take you through system operation from sample loading to electrical characterization. eFast Software automates the setup of the LEEN2 Column and controls key sub-systems ensuring consistent results in a multi-user production environment.

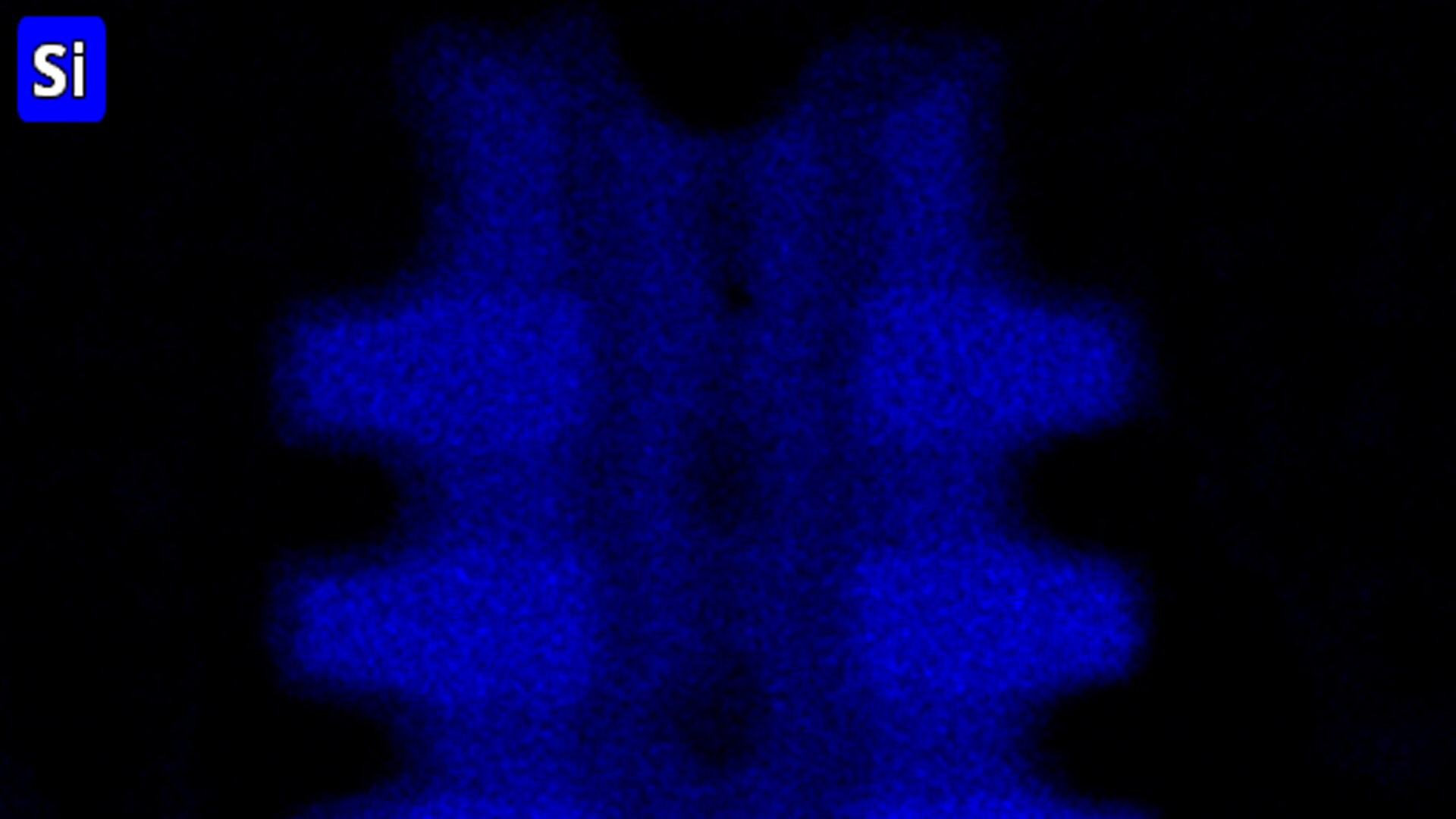

The nProber IV Systems can be equipped with EBIRCH2 and EBAC to find critical faults in 3D interconnect structures down to ~100 Ω. EBIRCH2 can also be used to localize critical defects in FinFET transistors.

In addition, the nProber IV System can be equipped with a sub-stage that enables probes to be separated by many millimeters, essential for the isolation of faults in large 3D NAND structures.

The nProber IV Systems can isolate resistive gate faults utilizing high-speed pulsed probing with rise times of less than 1 ns.

Our easyProbe Software automates key steps in the nProber IV workflow including: cleaning the probes, lowering the probes to the sample, and optimizing the electrical contact between the probes and the sample. easyProbe Software significantly reduces the training required to use the nProber IV System and allows for extended periods of unattended operation.

The optional Thermal Characterization Package supports the most recent automotive reliability standards. Samples temperatures can be controlled from -40°C to 150°C in order to isolate faults that are not detectable at ambient temperatures.

Performance, power efficiency, area, and cost are driving packaging innovations. Learn how workflows provide fast, precise, and accurate time-to-data.

Innovation starts with research and development. Learn more about solutions to help you understand innovative structures and materials at the atomic level.

Complex semiconductor device structures result in more places for defects to hide. Learn more about failure analysis solutions to isolate, analyze, and repair defects.

Many factors impact yield, performance, and reliability. Learn more about solutions to characterize physical, structural, and chemical properties.

Novel architectures and materials pose new challenges. Learn how to pinpoint faults and characterize materials, structures, and interfaces.

Nanoprobing

As device complexity increases, so does the number of places defects have to hide. Nanoprobing provides the precise localization of electrical faults, which is critical for an effective transmission electron microscopy failure analysis workflow.

Sample Preparation of Semiconductor Devices

Thermo Scientific DualBeam systems provide accurate TEM sample preparation for atomic-scale analysis of semiconductor devices. Automation and advanced machine learning technologies produce high-quality samples, at the correct location, and a low cost per sample.

Device Delayering

Shrinking feature size, along with advanced design and architecture, results in increasingly challenging failure analysis for semiconductors. Damage-free delayering of devices is a critical technique for the detection of buried electrical faults and failures.

Nanoprobing

As device complexity increases, so does the number of places defects have to hide. Nanoprobing provides the precise localization of electrical faults, which is critical for an effective transmission electron microscopy failure analysis workflow.

Sample Preparation of Semiconductor Devices

Thermo Scientific DualBeam systems provide accurate TEM sample preparation for atomic-scale analysis of semiconductor devices. Automation and advanced machine learning technologies produce high-quality samples, at the correct location, and a low cost per sample.

Device Delayering

Shrinking feature size, along with advanced design and architecture, results in increasingly challenging failure analysis for semiconductors. Damage-free delayering of devices is a critical technique for the detection of buried electrical faults and failures.

To ensure optimal system performance, we provide you access to a world-class network of field service experts, technical support, and certified spare parts.