Search Thermo Fisher Scientific

ELECTRICAL FAILURE ANALYSIS

ELITE System

Lock-In IR Thermography system for localization of defects in semiconductor devices.

Join the Conversation

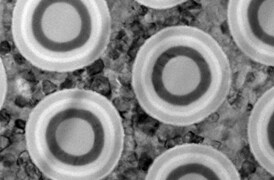

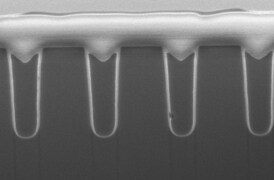

The rapid innovations in advanced 2.5D and 3D packaging, complex interconnect schemes, and higher-performance power devices are creating unprecedented failure localization and analysis challenges. Defective semiconductor devices often show a variation in the local power dissipation, leading to local temperature increases. The Thermo Scientific ELITE System utilizes lock-in IR thermography (LIT) to accurately and efficiently locate these areas of interest and provide non-destructive 3D device insights. The ELITE System’s optics and InSb camera are specifically designed to achieve high localization resolution and sensitivity and solve the most difficult analytical challenges.

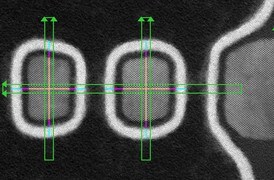

LIT, a form of dynamic IR thermography, provides maximum signal-to-noise ratio, increased sensitivity, and higher feature resolution compared to steady-state thermography. It is the ideal solution for the localization and analysis of line shorts, ESD defects, oxide damage, defective transistors, diodes, and device latch-ups. An optional laser scanning microscope enables high-resolution OBIRCH to complement the ELITE System’s thermal analysis capabilities.

The ELITE System is also available in the VX configuration, which provides all the features required for localizing defects in advanced power devices based on Si, SiC, or GaN technologies.

On-demand Spark Webinar: Semiconductor Packaging Challenges

- Very high sensitivity, InSb camera, and thermal emission optics enable nondestructive, through-package, and stacked die analysis

- Real-time lock-in measurement

- Contactless absolute temperature mapping

- Optical beam-induced resistance change (OBIRCH) option

- High-voltage power device analysis option (VX)

Lateral resolution |

|

Depth resolution |

|

| Defect types |

|

Sample types |

|

FOV |

|

DUT stimulation |

|

Time to results |

|

*Performance may vary depending on sample and specific setup.

Semiconductor Device Packaging

Advanced semiconductor device packaging requires new integration approaches and innovation in performance, power efficiency, area, and cost. See how Thermo Scientific failure analysis workflows provide fast, precise, and accurate time-to-data for device packaging development.

Semiconductor Pathfinding and Research

Advanced electron microscopy, focused ion beam, and associated analytical techniques for identifying viable solutions and design methods for the fabrication of high-performance semiconductor devices.

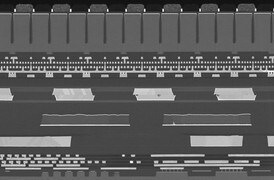

Yield Ramp and Metrology

We offer advanced analytical capabilities for defect analysis, metrology, and process control, designed to help increase productivity and improve yield across a range of semiconductor applications and devices.

Semiconductor Failure Analysis

Increasingly complex semiconductor device structures result in more places for failure-inducing defects to hide. Our next-generation workflows help you localize and characterize subtle electrical issues that affect yield, performance, and reliability.

ESD Semiconductor Qualification

Every electrostatic discharge (ESD) control plan is required to identify devices that are sensitive to ESD. We offer a complete suite of test systems to help with your device qualification requirements.

Power Semiconductor Device Analysis

Power devices pose unique challenges for localizing faults, primarily as a result of power device architecture and layout. Our power device analysis tools and workflows quickly pinpoint fault locations at operating conditions and provide precise, high-throughput analysis for characterization of materials, interfaces and device structures.

Display Module Failure Analysis

Evolving display technologies aim to improve display quality and light conversion efficiency to support applications in different industry sectors, while continuing to reduce production costs. Our process metrology, failure analysis and research and development solutions help display companies solve these challenges.

Physical and Chemical Characterization

Ongoing consumer demand drives the creation of smaller, faster, and cheaper electronic devices. Their production relies on high-productivity instruments and workflows that image, analyze, and characterize a broad range of semiconductor and display devices.

Thermal Fault Isolation

Uneven distribution of local power dissipation can cause large, localized increases in temperature, leading to device failure. We offer unique solutions for thermal fault isolation with high-sensitivity lock-in infrared thermography (LIT).

Thermal Fault Isolation

Uneven distribution of local power dissipation can cause large, localized increases in temperature, leading to device failure. We offer unique solutions for thermal fault isolation with high-sensitivity lock-in infrared thermography (LIT).

Electron microscopy services for

semiconductors

To ensure optimal system performance, we provide you access to a world-class network of field service experts, technical support, and certified spare parts.