Search Thermo Fisher Scientific

ELECTRICAL FAILURE ANALYSIS

ELITE System

Lock-In IR Thermography system for localization of defects in semiconductor devices.

Join the Conversation

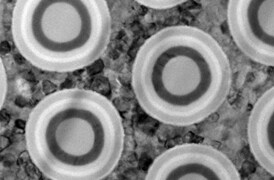

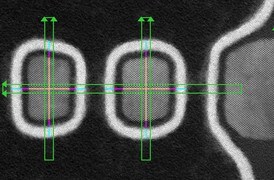

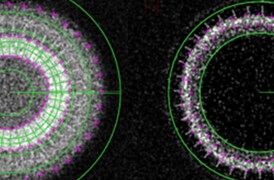

The rapid innovations in advanced 2.5D and 3D packaging, complex interconnect schemes, and higher-performance power devices are creating unprecedented failure localization and analysis challenges. Defective semiconductor devices often show a variation in the local power dissipation, leading to local temperature increases. The Thermo Scientific ELITE System utilizes lock-in IR thermography (LIT) to accurately and efficiently locate these areas of interest and provide non-destructive 3D device insights. The ELITE System’s optics and InSb camera are specifically designed to achieve high localization resolution and sensitivity and solve the most difficult analytical challenges.

LIT, a form of dynamic IR thermography, provides maximum signal-to-noise ratio, increased sensitivity, and higher feature resolution compared to steady-state thermography. It is the ideal solution for the localization and analysis of line shorts, ESD defects, oxide damage, defective transistors, diodes, and device latch-ups. An optional laser scanning microscope enables high-resolution OBIRCH to complement the ELITE System’s thermal analysis capabilities.

The ELITE System is also available in the VX configuration, which provides all the features required for localizing defects in advanced power devices based on Si, SiC, or GaN technologies.

On-demand Spark Webinar: Semiconductor Packaging Challenges

- Very high sensitivity, InSb camera, and thermal emission optics enable nondestructive, through-package, and stacked die analysis

- Real-time lock-in measurement

- Contactless absolute temperature mapping

- Optical beam-induced resistance change (OBIRCH) option

- High-voltage power device analysis option (VX)

Lateral resolution |

|

Depth resolution |

|

| Defect types |

|

Sample types |

|

FOV |

|

DUT stimulation |

|

Time to results |

|

*Performance may vary depending on sample and specific setup.

Desenvolvimento e localização de semicondutores

Microscopia eletrônica avançada, feixe de íon focalizado e técnicas analíticas associadas para identificar soluções viáveis e métodos de desenho para a fabricação de dispositivos semicondutores de alto desempenho.

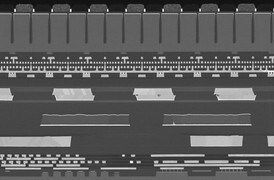

Rampa de escoamento e metrologia

Oferecemos recursos analíticos avançados para análise de defeitos, metrologia e controle de processos projetados para ajudar a aumentar a produtividade e melhorar o rendimento em uma variedade de aplicações e dispositivos semicondutores.

Análise de falha de semicondutores

Estruturas de dispositivos semicondutores cada vez mais complexas resultam em mais locais onde defeitos que induzem falhas podem se ocultar. Nossos fluxos de trabalho de última geração o ajudam a localizar e caracterizar problemas elétricos sutis que afetam o rendimento, o desempenho e a confiabilidade.

Qualificação de semicondutores ESD

Cada plano de controle de descarga eletrostática (ESD) é necessário para identificar dispositivos sensíveis à ESD. Oferecemos um conjunto completo de sistemas de teste para ajudar com os requisitos de qualificação do seu dispositivo.

Caracterização física e química

A demanda contínua dos consumidores impulsiona a criação de dispositivos eletrônicos menores, mais rápidos e mais baratos. Sua produção depende de instrumentos e fluxos de trabalho de alta produtividade que fazem imagens, analisam e caracterizam uma ampla gama de semicondutores e dispositivos de exibição.

Isolamento de falha térmica

A distribuição desigual da dissipação de energia local pode causar grandes aumentos localizados de temperatura, causando a falha do dispositivo. Oferecemos soluções exclusivas para isolamento térmico de falhas com termografia por infravermelho (LIT) de alta sensibilidade.

Isolamento de falha térmica

A distribuição desigual da dissipação de energia local pode causar grandes aumentos localizados de temperatura, causando a falha do dispositivo. Oferecemos soluções exclusivas para isolamento térmico de falhas com termografia por infravermelho (LIT) de alta sensibilidade.

Serviços de microscopia eletrônica para

semicondutores

Para garantir o desempenho ideal do sistema, fornecemos acesso a uma rede de especialistas em serviços de campo, suporte técnico e peças de reposição certificadas.